在先进封装领域,热敏感性对高性能芯片组件带来巨大挑战,加剧了各类物理效应影响,增加了互连难度及设计成本与周期,也催生了对新型设计工具的迫切需求。

过去,组件多集成于较厚基板的平面 SoC;如今,主板持续变薄以缩短信号传输距离,这降低了传统硅基板效能,导致晶格畸变、翘曲,以及冷热不均现象。这些问题会引发互连线故障,影响微凸块连接稳定性,进而造成性能下滑、良率降低。

当芯片运行发热时,不同材料膨胀速率差异产生应变,引发翘曲、开裂或分层等问题,严重影响电气性能与互连可靠性。随着设备封装密度提升,结构尺寸缩小且材料种类增多,热膨胀系数(CTE)差异带来的挑战愈发显著。

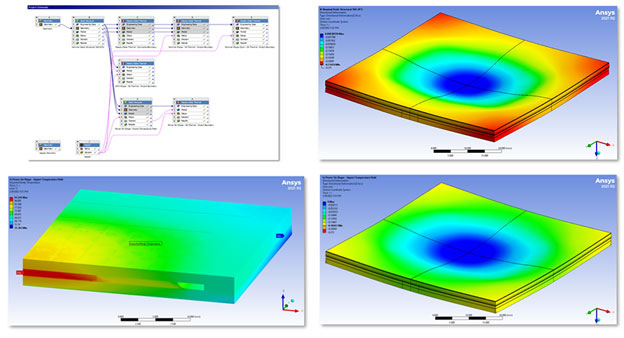

左上:Ansys原理图,显示耦合热模型和结构模型的子系统。右上:20°C下的封装翘曲,死虫视图(观察底座底部)。右下:施加“通电”热尖端后的封装翘曲,死虫视图(与20°C下的封装翘曲相同的色标)。左下:来自Icepak的温度曲线边界条件。

针对这些问题,可采取多种缓解应力的方法。在材料选择上,优先采用热膨胀系数与芯片接近的基底材料,如陶瓷基片;选用低弹性模量的环氧树脂等柔韧性封装材料,缓冲外部应力;使用高导热率的散热材料,像铜铝及其合金、碳化硅颗粒增强铝基复合材料,加快热量散发,降低热应力。在结构设计方面,合理布局芯片,将发热量大的芯片分散放置,把敏感芯片置于应力较小区域;设置弹性缓冲垫、特殊支撑结构等缓冲组件,吸收分散应力;优化封装外形,采用圆形或椭圆形设计减少应力集中。在工艺设计上,精确控制倒装芯片键合的温度、压力和时间,优化固化工艺的温度曲线与时间,合理安排制造工艺顺序,避免对已键合芯片产生额外应力。

工程师在封装设计早期常借助有限元分析(FEA)工具,评估芯片封装交互(CPI)产生的应变场。由于热、机械、电效应间关联性增强,多物理场仿真成为关键。通过模拟先进封装内部物理过程,可在生产前预测故障,避免损失。同时,采用 CTE 匹配材料、优化键合技术、整合多物理场分析,也有助于解决相关问题。

在 Chiplet 设计中,芯片间布线密度显著降低,为维持带宽需付出更高成本,且会带来功耗增加、延迟上升等问题。因此,架构设计时需综合考量数据接口位置、流量模式、延迟与吞吐量要求,确保设计契合应用需求。

3D - IC 中芯片堆叠数量增加,进一步加剧设计挑战。在供电网络设计、PCB 组装等环节,都需从系统层面综合考虑,避免热撕裂等问题影响封装可靠性。传统的阈值分析方法虽被广泛应用,但存在过度设计问题。更精准的逐器件或区域分析方法,将成为未来趋势。

此外,材料特性与制造工艺对封装应变影响重大,需与代工厂等紧密合作获取准确数据。通过 X 射线或光学技术监测芯片翘曲,结合数字孪生等虚拟测试手段,可有效评估可靠性。

为了避免3D-IC和多芯片设计中出现应变和过敏问题,行业专家强调了以下关键领域:

早期热分析和规划。热问题需要在设计过程的早期就考虑,而不是事后才考虑。热分析应该成为架构架构探索和规划阶段的一部分。

全栈建模。工程师能够需要对整个多芯片堆栈进行建模和分析,包括芯片、内层、封装和PCB。

芯片间的热连接。在一些芯片设计中,需要考虑芯片间的热连接。一个芯片的热量会影响相邻的芯片。

不同的材料和热膨胀系数(CTE)。使用具有不同热膨胀系数(CTE)的材料可能会导致界面问题。这些问题需要进行建模和分析。

模型凸块、TSV和芯片间接口。需要仔细建模和分析凸块、硅通孔(TSV)和芯片间按键合接口等3D结构中的应力/变形。

电磁(EM)建模。在高速下,电磁效应变得很重要,需要完整的电磁建模,而不仅仅是RC建模。

电力分配。正确的电力分配网络设计是为了控制热量和避免热点关键。

多物理场仿真。热效应、机械效应和电效应相互关联。需要多物理场仿真工具来捕捉这些交互。

由于应变和应变已成为先进封装设计中的关键考虑因素,需要建模相应和分析方法来确保可靠和高性能的集成系统。

集成正在推动芯片和封装设计人员在架构规划阶段就多物理场效果,例如应变、应变、热性能、SI/PI。随着设计的成熟,进一步的验证确保最终可以满足产品满足操作和可靠性要求。EDA 供应商在并提供互联的架构、设计和多物理场仿真及验证工具/工作方面发挥着关键作用,使封装架构师能够重新对工艺、布局和材料选择做出正确的决策。